1.概要

システムクロックを240MHzに設定してLチカ

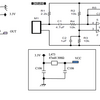

USBのクロック設定も行う

2.クロック設定

1)Clock configuration register 構成と設定

(1)クロック設定レジスタ

STM32Fx : RCC_CFGR

AT32F4x : CRM_CFG

・名前は違うがアドレスは同じ 0x4002-1004

・STM32F1x の Reserved エリアを使って拡張

拡張詳細はAT32F4xのリファレンスマニアル参照

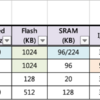

(2)240MHz 設定

STM32F103 72MHz から最小限の変更で設定

|

アイテム |

STM32F103 |

AT32F403A |

変更内容 |

|

|

HCLK |

72MHz |

240MHz |

CRM_CFG. PLLRANGE bit31 = 1: PLL output > 72 MHz CRM_CFG.PLLMULT[5:0] bit30:29,21:18 = 011101:PLLx 30 |

0x4002-1004 |

|

ADC |

12MHz |

20MHz |

CRM_CFG.ADCDIV[2:0] bit28,15:14 = 101:PCLK/12 |

↑ |

|

USB |

HSE 48MHz |

HIS 48Mhz |

CRM_MISC1.HICLDIV bit25 = 1: HICK |

0x4002-1030 |

|

CRM_MISC3. HICK_TO_USB bit8 = 1: HICK or HICK/6 |

0x4002-1054 |

|||

|

ACC_CTRL1. ENTRIM bit1 = 1: HICKTRIM is calibrated. ACC_CTRL1. CALON bit0 = 1: Calibration enabled, and starts searching for a pulse on the USB_SOF. |

0x4001-580C |

・設定メモ

CRM 0x4002 -1000

CRM_CFG: -0004 初期値=0x0000

CRM_MISC1: -0030

CRM_MISC3: -0054

*(__IO uint32_t *)0x40021004 = 0x001D840A→0xB035440A

0000 0000 0001 1101 1000 0100 0000 1010

1011 0000 0011 0101 0100 0100 0000 1010

31 27 23 19 15 11 7 3

(3)Clock configuration register (CRM_CFG) 設定表

2)Clock tree 設定

(1)STM32F1xとの比較

(2)AT32F4x

3.クロック再設定手順

STM32F1x_Reference manual 8.2.3 PLLs によるとPLL動作中は設定変更できないためPLLを停止して変更後PLL再起動する

|

処理 |

設定値 |

|

|

System ClockをHISに待避 |

RCC_CFGR Bit 1:0 SW[1:0]:SystemclockSwitch |

00: HSI selected as system clock |

|

PLL停止 |

RCC_CR Bit 24 PLLON:PLLenable |

0: PLL OFF |

|

PLL停止待ち |

RCC_CR Bit25 PLLRDY:PLLclockreadyflag |

wait 0: PLL unlocked |

|

PLL再設定 |

RCC_CFGR |

240MHz設定 (RCC_CFGR_SW = 00) |

|

PLL起動 |

RCC_CR Bit24 PLLON:PLLenable |

1: PLL ON |

|

PLL起動待ち |

RCC_CR Bit25 PLLRDY:PLLclockreadyflag |

wait 1: PLL locked |

|

System ClockをPLLCLKに戻す |

RCC_CFGR Bit 1:0 SW[1:0]:SystemclockSwitch |

10: PLL selected as system clock |

|

USBクロック設定 |

|

HICK 48MHz |

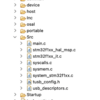

4.コード

1)User CODE SysInit

・240MHz システムクロック設定

・48MHz 内蔵USBクロック設定

- もっと読む

コメントを書く